Newsletter 02/2021

Während sich hochvolumige Chipaufträge relativ schnell von den jüngsten Lieferengpässen erholen dürften, stehen Besteller kleiner und mittlerer IC-Mengen vor einem steinigen Weg. Unser Experte Andy Heinig zeigt einen Lösungsansatz für dieses Problem auf.

Fast täglich wird mittlerweile von der Knappheit bei Schaltkreisen berichtet. Aktuell betrifft das vor allem Automobilhersteller, aber auch andere Systemhersteller z. B. im Maschinenbau haben damit zu kämpfen. Selbst Hersteller von Massenartikel wie Spielkonsolen berichten von denselben Problemen. Allerdings wird das Problem bei den Massenartikeln sicherlich recht schnell gelöst, indem die Produktion bei den Schaltkreisherstellern auf die dafür nötigen Schaltkreise gelenkt wird, um in diesem Bereich hohe Strafzahlungen und auch einen Reputationsverlust in der Außendarstellung zu vermeiden. Ganz anders aber stellt sich die Situation für Anbieter von Produkten im kleineren Mengenbereich dar, die ebenfalls – auf neueste Fertigungstechnologien aufbauende – Schaltkreise benötigen. Da die Hersteller der Schaltkreise sich in der nächsten Zeit auf die hochvolumigen Produkte konzentrieren, werden alle andere Schaltkreise in der Fertigung und Auslieferung noch weitere Verzögerungen erfahren. Dieser Zustand kann in Zukunft durch neue Fertigungsstätten reduziert werden, aber auch deren Errichtung wird noch einige Jahre in Anspruch nehmen, in denen die Knappheit kleinerer und mittlerer IC-Stückzahlen weiter bestehen bleiben wird. Selbst wenn die Gesamtsituation danach verbessert sein sollte, werden die Schaltkreisanbieter auch in weiteren Konjunkturhochphasen mit denselben Problemen zu kämpfen haben. Dabei geht es noch nicht einmal nur um die Produktion, auch bei dem nötigen Engineering seitens der Halbleiterhersteller bis zum Produktionsstart werden diese ICs nicht die höchste Priorität genießen.

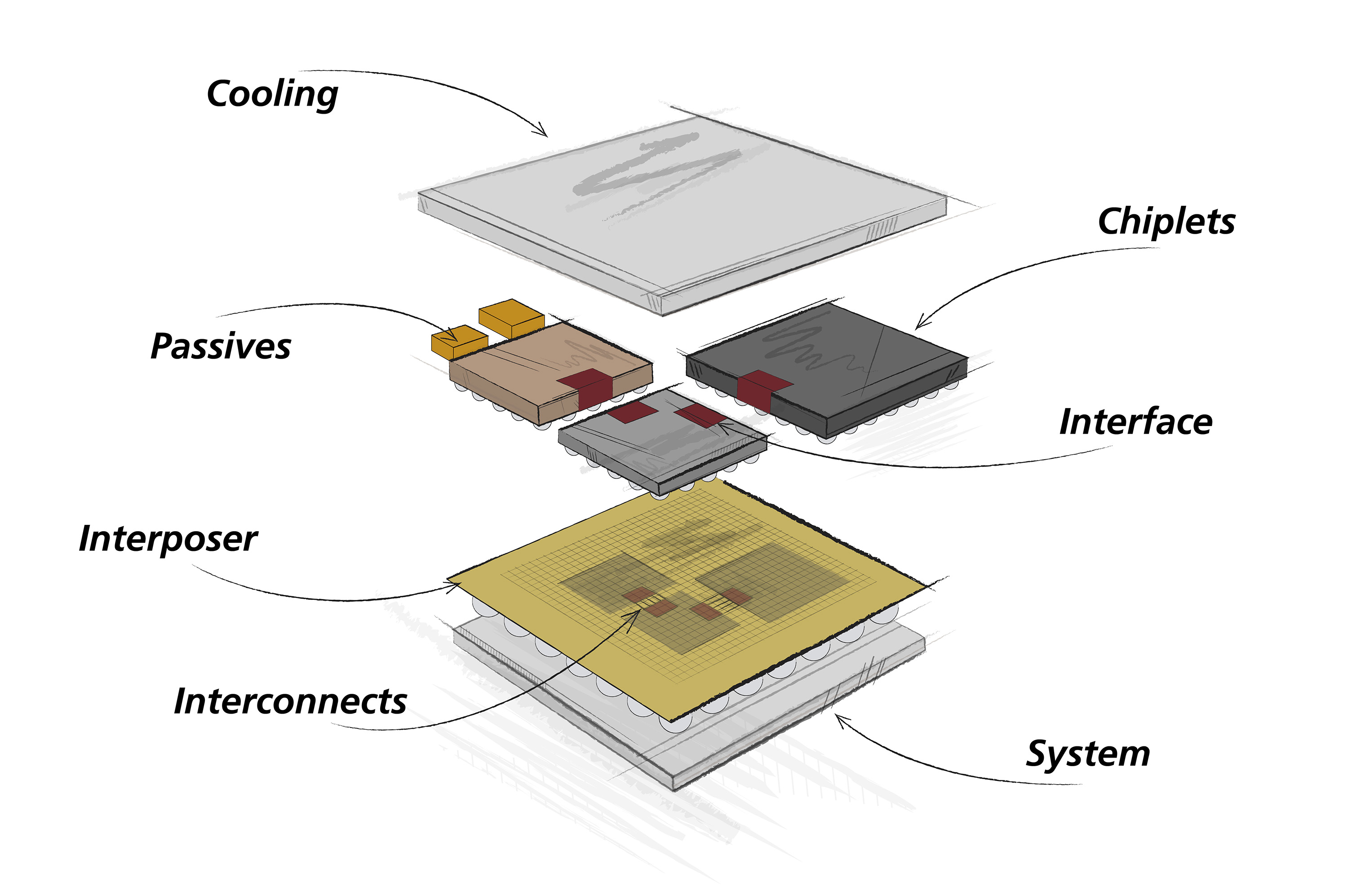

Einen möglichen Ausweg könnten in Zukunft neuartige Packaging-Lösungen wie zum Beispiel die Chiplets bringen. Ihre Integration erlaubt das Aufteilen der Funktionalität auf mehrere Schaltkreise in einem Gehäuse. Damit kann die Funktionalität, die neuartige Fertigungstechnologien benötigen, auf einige wenige Schaltkreise konzentriert werden. Wenn diese, wie das aktuell der Fall ist, für jedes Projekt spezifisch designt werden müssen, ist keine Verbesserung der Verfügbarkeit zu erwarten. Wenn allerdings für diese besonderen Schaltkreise des Chiplets eine Vereinheitlichung erfolgen kann, dann könnten sie in unterschiedlichen Projekten zum Einsatz kommen. Damit würde sich einerseits die Anzahl der benötigten Schaltkreise erhöhen, womit sie auf einmal von größerer Bedeutung bei dem Hersteller der Schaltkreise wären, was auch die Verfügbarkeit erhöhen würde. Auf der anderen Seite würden sich als Nebeneffekt die Designkosten verringern, da ja die Schaltkreise nicht immer wieder neu designt werden müssten, sondern in verschiedenen Chiplet-Projekten direkt eingesetzt werden könnten.

Um dahin zu kommen, sind verschiedene Schritte nötig. Auf der einen Seite müsste als erstes ein einheitliches Interface sowohl auf der elektrischen als auch auf der Signalebene definiert werden. Dazu sind erste Standards in Entwicklung. Allerdings ist ihre Eignung für den oben genannten Anwendungsfall noch nicht geklärt. Einige der Entwicklungen für entsprechende Standards sind spezifisch für Beschleunigerkarten, die neben einem Prozessor arbeiten, definiert und haben dann ihre Stärken genau für diesen Anwendungsfall. Das kann in der Definition des Standards auch bedeuten, dass Zugriffe auf entfernte Speicherbereiche möglich und dabei auch bezüglich der Zugriffsrechte abgesichert sind. Das sind aber meistens keine Anforderungen, die in den oben beschriebenen Applikationen und Anwendungen benötigt werden.

Weiterhin muss aber neben dem Interface auch die Funktionalität des Schaltkreises definiert werden. An der Stelle wird es vermutlich noch schwieriger, einheitliche Standards zu finden, die viele verschiedene Anwendungsklassen abdecken. Auf der einen Seite könnte man das Problem mit kleingranularen Schaltkreisen lösen, dann wäre man sehr flexibel, aber hätte dann auch viele Interfaces zwischen den Schaltreisen mit entsprechendem Platzbedarf sowie auch viel Integrationsaufwand für die entsprechenden Schaltkreise in das Chiplet. Wenn man auf der anderen Seite die Schaltkreise zu grobgranular definiert und designt, hat man wenige Interfaces, aber dafür auch wenig Flexibilität beim Aufbau komplexerer Systeme. Das kann dann zu Situationen führen in der die entsprechende Funktionalität des komplexen Systems gar nicht oder nur unter Verwendung von viel unbenutzter Kapazität der Schaltkreise realisiert werden kann. Zweiteres führt dann zu großen Gesamtaufbauten bei den Chiplets mit entsprechenden Kosten des Gesamtsystems.

Sollten aber die entsprechenden Standards definiert werden können, sowohl bei den Schnittstellen zwischen den Schaltkreisen der Chiplets als auch bei der Funktionalität der wesentlichen – vor allem in neuartigen Technologien gefertigten – Schaltkreise der Chiplets, dann kann der Ansatz zukünftig eine Möglichkeit bieten, die Industrie im Bereich kleiner und mittlerer Stückzahlen von hochintegrierten Systemen sicher und ohne Lieferprobleme zu versorgen.

Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme

Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme