Newsletter 02/2021

Whereas high-volume chip orders are likely to recover from the recent supply bottlenecks relatively quickly, companies looking to purchase ICs on a small or medium scale face the prospect of an uphill struggle. Our expert Andy Heinig examines a potential solution for this problem.

These days, there are new reports on the shortage of chips almost every day. Currently, this issue is affecting mainly car manufacturers such as Audi, Ford and more. But other system manufacturers, such as in the machine construction industry, are also facing this challenge. Even manufacturers of mass-produced articles such as game consoles are reporting the same problems. The problem is sure to solve itself quickly for mass-produced articles by shifting production (at the chip manufacturer’s facilities) to the required chips in order to avoid high penalties or loss of reputation and image in this sector. But the situation is very different for providers of products in smaller quantities that also require chips based on the latest production technology. As chip manufacturers will be focusing on high-volume products in the near future, all other chips will continue to see delays in production and delivery. In the future, this state of affairs can be counteracted with new production sites, but their construction takes at least 2 to 3 years, a time during which the shortage of small and medium-sized IC orders won’t cease to exist. Even if the overall situation improves after this, chip providers will still face the same problems in further economic peaks. But it’s not just production – these ICs won’t be given the highest priority by semiconductor manufacturers in terms of the necessary engineering until they are ready for production.

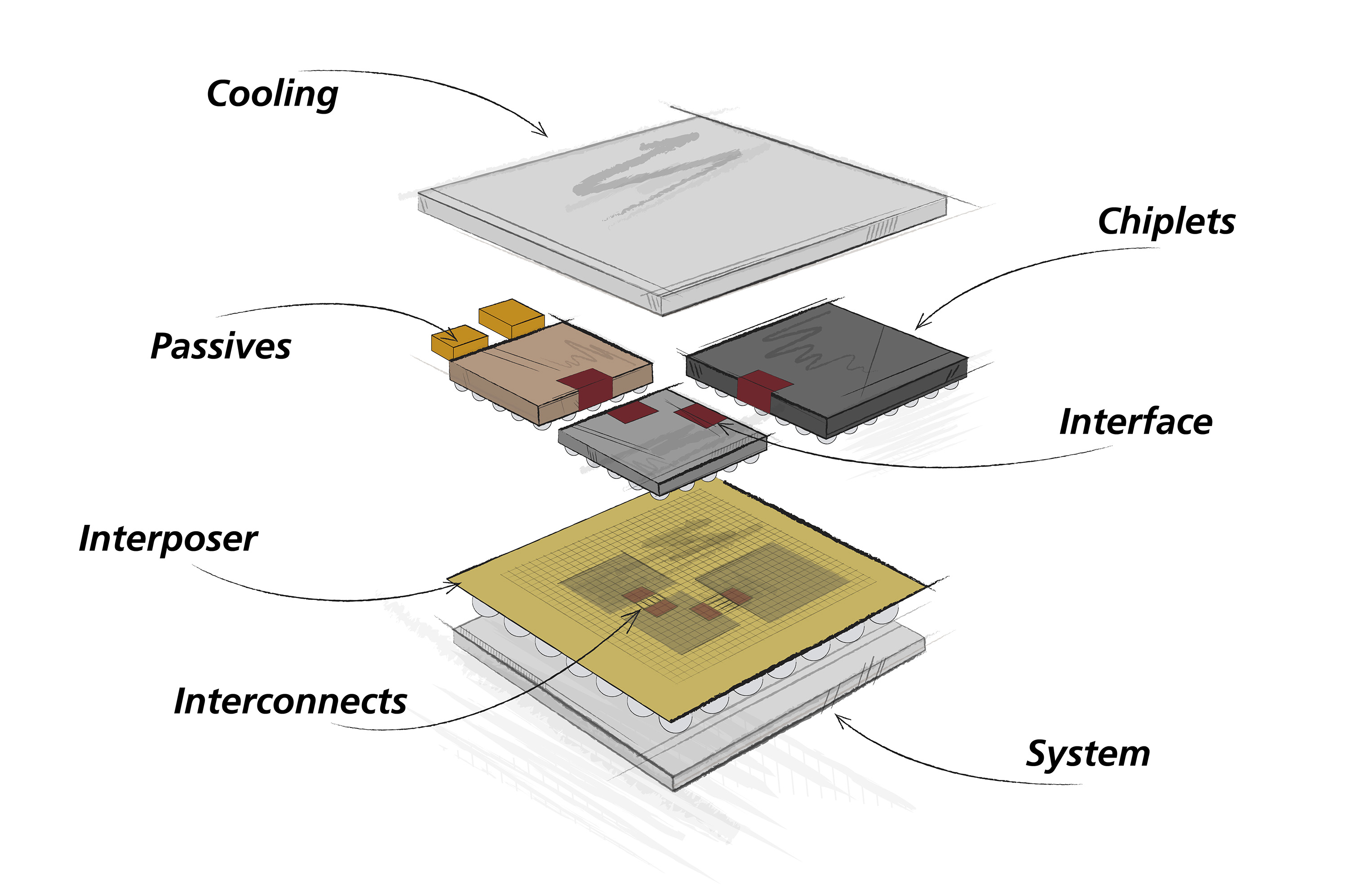

One possible alternative in the future could be innovative packaging solutions, like that of chiplets. Their integration enables functions to be spread across multiple functional circuit block in one package, allowing the functionality requiring state-of-the-art production technology to be concentrated into just a few circuits. If they have to be designed specifically for each project, as is currently the case, no improvements to availability can be expected. But if the special chiplet ICs can be standardized, they could be used in a wide range of different projects. On the one hand, this would increase the number of required ICs, meaning that they would suddenly become more significant to semiconductor manufacturers, also increasing availability. On the other, this would also reduce design costs, as the circuits wouldn’t have to be redesigned over and over again, but could instead simply be used in different chiplet projects.

There are various steps required to reach this point. First, a standard interface would have to be defined on both the electrical and signal levels. Initial standards are currently being developed. However, it’s not clear whether they are suitable for the applications named above. Several developments for such standards are defined specifically for accelerator cards working in tandem with a processor and their strengths reflect this precise application. In the standard definition, this can also mean that access to remote memory is possible and safeguarded by means of access rights. But this is often not a requirement needed in the applications described above.

Furthermore, the function of the chip also has to be defined in addition to the interface. Here, it is likely even more difficult to find uniform standards that cover many different application classes. On the one hand, the problem could be solved with fine-grained circuits, which would enable a high degree of flexibility but entail many different interfaces between the circuits (and therefore take up a lot of space) while requiring more effort to integrate the corresponding circuits into the chiplet. On the other hand, if the circuits are defined and designed to be too coarse-grained, the result is fewer interfaces, but also less flexibility in building more complex systems. This can lead to situations where the functionality of the complex system cannot be realized at all, or only by using a lot of unused circuit capacity. The latter results in large overall chiplet designs with high overall system costs.

If the relevant standards can be defined for both the interfaces between the chiplets and the functionality of the essential chiplet circuits primarily produced using state-of-the-art technologies, this approach may offer a way to reliably equip the industry with small and medium quantities of highly integrated systems without supply problems.

Fraunhofer Institute for Integrated Circuits IIS, Division Engineering of Adaptive Systems EAS

Fraunhofer Institute for Integrated Circuits IIS, Division Engineering of Adaptive Systems EAS