Newsletter 04/2019

Andy Heinig über Chiplets als den neuen Packaging-Ansatz, der Elektronik für das autonome Fahren auch unter komplexen Bedingungen ermöglichen wird.

Oberklasse-Fahrzeuge, die auf Autobahnen autonom fahren können, sind bereits auf den Markt gekommen oder werden in den nächsten Jahren in den Markt eingeführt. Die Fahrt auf der Autobahn wurde als erste Anwendung ausgewählt, da die Anzahl von zu berücksichtigenden Objekten vor, neben und hinter dem Auto überschaubar ist. Damit ist die benötigte Rechenleistung abschätzbar und mit aktuellen Hochleistungs-Rechenplattformen realisierbar. Wenn die Rechenleistung einer solchen Plattform nicht ausreicht, kann diese kaskadiert werden.

Im Gegensatz zum autonomen Fahren auf der Autobahn müssen in komplexen Umgebungen, z. B. in der Stadt deutlich mehr Objekte erkannt werden. Aktuelle Abschätzungen gehen von bis zu 400 Objekten aus, die gleichzeitig registriert werden müssen. Allerdings gibt es dafür keine Obergrenze und in einigen Situationen kann die Zahl auch noch überschritten werden. Damit ist die Rechenleistung nur schwer abzuschätzen, da sie stark mit der Umgebungssituation korreliert. Allerdings ist sicher, dass aktuelle Hochleistungs-Plattformen für autonomes Fahren diese Rechenleistungen nicht zur Verfügung stellen können.

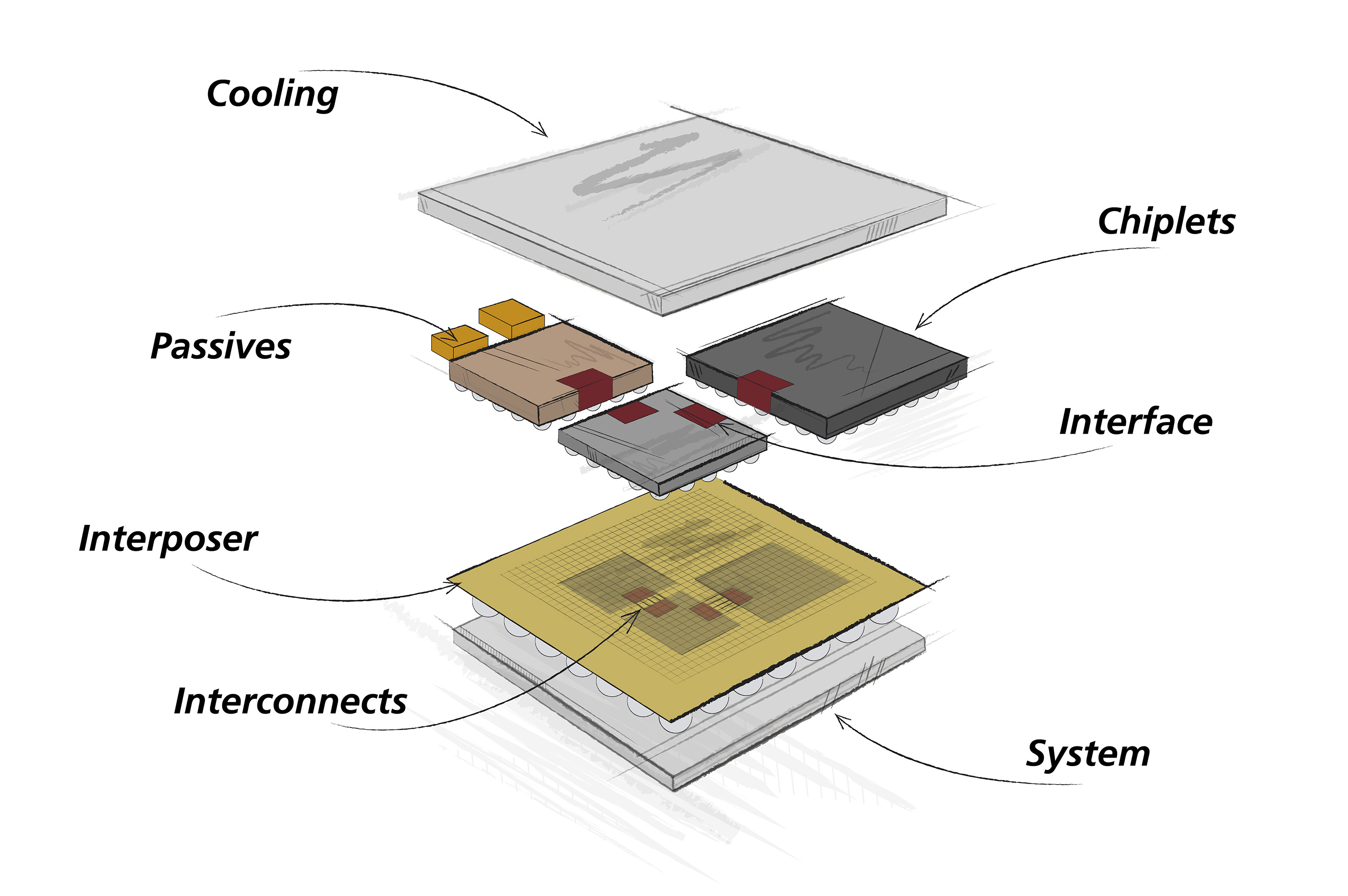

Daher wird ein Ansatz in der Systemarchitektur benötigt, der diese Rechenleistung perspektivisch realisierbar macht. Dafür stehen verschiedene Möglichkeiten zur Verfügung. Auf der einen Seite können komplexe System-on-Chips (SoCs) implementiert werden. Auf der anderen Seite können neuartige Ansätze aus dem Bereich des Packaging zum Einsatz kommen, wie die Chiplets. Bei diesen können verschiedene Schaltkreise auf einem Package-Substrat montiert werden wie bei einem System-on-Package (SiP). Allerdings ist bei den Chiplets im Gegensatz zu SiP auch die Schnittstelle zwischen den Schaltkreisen spezifiziert und vereinheitlicht. Damit können vorgefertigte Schaltkreise mehr oder weniger beliebig zu – aus Sicht der Applikation – immer neuartigen Systemen zusammengefügt werden.

Der Chiplet-Ansatz hat aus Sicht der Entwickler autonomer Fahrzeuge verschiedene Vorteile. Nach aktuellem Stand wird das autonome Fahren über verschiedene Zwischenschritte eingeführt bzw. werden Mittelklassewagen in der nächsten Zeit nur teilautonomes Fahren erlauben. Damit stellt sich die Herausforderung, dass für verschiedene Fahrzeugklassen unterschiedliche Rechenleistungen und Systemschnittstellen zur Verfügung gestellt werden müssen. Diese Anforderung ist mit einem modularen Ansatz wie den Chiplets deutlich einfacher zu erfüllen als mit einem monolithischen wie den SoCs. Daher gibt es in der Automobilindustrie aktuell Diskussionen, die Chipletentwicklung schneller voranzubringen.

Allerdings werden bei der Implementierung von Chiplets im Bereich des autonomen Fahrens wahrscheinlich andere Anforderungen an die Schnittstelle zwischen den Schaltkreisen existieren als bei aktuell diskutierten Standards. Daher ist es wichtig, für dieses Einsatzgebiet eine eigene Schnittstellendefinition voranzutreiben oder beide Aktivitäten in Einklang zu bringen. Aus diesem Grund sind einige Treiber der Chiplet-Technologie, wie das Fraunhofer IIS/EAS, bei verschiedenen Standardisierungsaktivitäten involviert.

Darüber hinaus wird die immer weitere Verbreitung des autonomen Fahrens auch deutlich höhere Anforderungen an die Integrationstechnologie stellen. Die Datentransferrate zwischen den Schaltkreisen wird sehr groß sein, da viel mit Bild- und Radardaten gearbeitet wird, die pro Zeiteinheit zu großen Datenmengen führen. Diese müssen dann in den Schaltkreisen des Chiplets verarbeitet und deshalb immer wieder zwischen den Schaltkreisen ausgetauscht werden. Hieraus resultiert die Forderung an hohe Datenraten, die nur mit schnellen und massiv parallelen Schnittstellen realisiert werden können. Dafür muss auch die Package-Technologie vorbereitet sein. Nur Ansätze wie 2.5-D-Integration (Interposer) oder Fan-out-Technologien können diese Anforderungen erfüllen.

Und auch von Seiten der Verifikation sind neue Ansätze nötig. Vor allem im Bereich der Signalintegrität der Leitungen zwischen den Schaltkreisen und im Bereich der Power/Ground Versorgung sind weitere zusätzliche Simulationen und Analysen unumgänglich.

Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme

Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme