Leistungsangebot nach Geschäftsfeldern

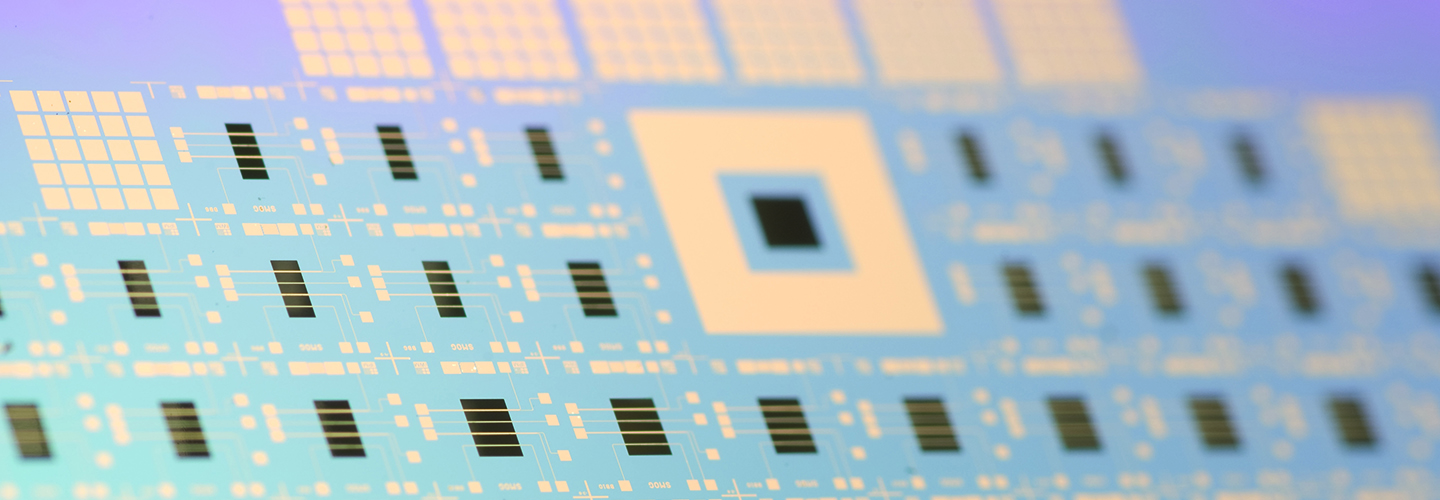

Wir entwickeln Lösungen für die Wirtschaft in den Geschäftsfeldern »Entwurfsmethoden«, »Effiziente Elektronik« sowie »Verteilte Analyse- und Regelsysteme«. Basis hierfür sind unser fundiertes Fachwissen in den verschiedenen Forschungsthemen und die Ergebnisse aus Forschungsprojekten in unterschiedlichen Anwendungsfeldern.

Unser Ziel ist es, unsere Kunden bei der Entwicklung von qualitativ hochwertigen Produkten und effizienten Prozessen maßgeblich zu unterstützen. Hierfür entwickeln unsere Ingenieure und Naturwissenschaftler unter anderem leistungsfähige Sensorsysteme und Technologien für die vernetzte Automatisierung in der Produktion. Darüber hinaus widmen sie sich dem Entwurf zuverlässiger und robuster elektronischer Systeme sowie der automatischen Analyse großer Datenmengen.

Unsere Unterstützung reicht von der Beratung und dem Durchführen von Machbarkeitsstudien über die Entwicklung von Elektronikkomponenten und leistungsfähigen Algorithmen bis hin zur Überleitung von Technologien in die Fertigung. Abgerundet wird unser Angebot durch zahlreiche Schulungsangebote nach Kundenwünschen.

Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme EAS

Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme EAS